# A Low-Cost Fabrication Route for Silicon Microchannels and Microgratings with Flow-Enabled Polymer Self-Assembly Patterning and Wet Etching

Liyi Li<sup>1</sup>, Bo Li<sup>1</sup>, Zhiqun Lin<sup>1</sup>, Ching-Ping Wong<sup>1,2</sup>\*

- 1. School of Materials Science and Engineering, Georgia Institute of Technology, Atlanta, GA, USA

- 2. Department of Electronic Engineering, The Chinese University of Hong Kong, Shatin, HongKong \*Corresponding author: cpwong@cuhk.edu.hk

#### **Abstract**

Microchannels and microgratings on silicon (Si) are key components for microfluidic device, microelectromechanical system, Si photonics, micro-chemical reactor, microbiomedical devices and other applications. In the fabrication flow of these microstructures, photolithography and dry etching are the two major steps. However, both of them incur high fabrication cost. In this paper, we introduce a novel approach for fabrication of Si microstructures. The approach uses flow-enabled polymer self-assembly (FESA) as a facile pattern formation method on Si surface; a novel wet etching method, named metal-assisted chemical etching, is employed for Si etching. These two consecutive steps show good compatibility with each other and capability of uniform microstructures fabrication on Si. The proposed approach, with combination of two low-cost yet high-performance novel technology, will serve as a promising route for microchannels and microgratings fabrication for various Si-related devices in high-volume production.

### 1. Introduction

Microchannels and microgratings on silicon (Si) substrate are basic components in many Si-related technology. For example, microchannels play the key role in the fast growing microfluidic technology. By confining the flow liquid and gas liquid in micrometer scale, microchannels enable unique functions of the devices, such as in-system cooling [1, 2], microscale chemical and biochemical processing [3, 4]. Microchannels are heart of also the most microelectromechanical system (MEMS) device [5-7]. For microgratings, they have been widely used in the silicon optical devices [8, 9]. Fabrication of microchannels and microgratings share the similar key steps: pattern formation and Si etching. In the pattern formation step, a mask layer with designed geometry is fabricated on the Si surface. A certain portion of the mask layer is made hollow so that bare Si surface is exposed. In the following Si etching step, the bare Si without coverage of the mask layer is selectively etched, while those covered by the mask layer is passivated from etching.

The most widely used pattern formation method is photolithography, which is readily available in microelectronic industry for integrated circuits (ICs) fabrication. In photolithography, a layer of photosensitive materials, i.e. the photoresist, is put on the Si surface by either spin coating or lamination. After baking at elevated temperature, the Si sample is exposed under UV-visible light with a photomask.

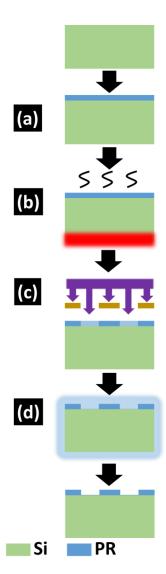

After developing, photoresist is partially dissolved and the pattern on the photomask is transferred on the photoresist. Photolithography possesses high pattern transfer fidelity and high resolution down to sub-micrometer. The tools and materials for photolithography are widely available in the industry. However, they require high investment. In addition, the baking and developing processes are essentially high energy consuming and release a considerable amount of harmful waste (Figure 1).

On the other hand, several non-photolithographic patterning methods have been developed, such as nanoimprint lithography (NIL) [10, 11] and soft lithography [12, 13]. In a typical NIL experiment, a layer of thermoplastic polymer is put on the Si surface. Then a hard template with the pattern topologically engraved on the surface is pressed against the polymer and the sample is heated so that the polymer layer undergoes glass transition and replicates the geometry of the template after cooling down. In soft lithography, soft templates are used for the pattern transfer. Certain materials (metal, polymer or biomolecules) are directly loaded on the soft templates and transferred on Si by contact printing. In both NIL and soft lithography, the UV-visible light exposure step is eliminated and the overall cost is lowered. However, fabricating the template is still expensive.

It has long be known that nanoscale materials could form highly ordered micro- or nanostructures on Si through selfassembly. For example, driven by thermodynamic force, silica [14] or polymer [15, 16] nanospheres tend to densely pack themselves into hexagonal 2D lattice. The lattice parameter is defined by the diameter of the nanospheres, and no external template is required. Recently, block copolymer (BCP) have been proposed as candidate for nanolithography [17-19]. BCP are polymers that possess two or more different blocks in one polymer chains. such poly-(styrene-blockas methylmethacrylate). Due to the distinct chemical properties of each block, their interaction with the Si as well as neighboring blocks are different, which drives the whole polymer chain to align themselves. The collectively selfassembly of polymer chains could form ordered structures. The dimension of each repeating unit in the ordered structures is defined by the chemical structure of the BCP molecules, thus the nanoscale morphology of the BCP self-assembly does not require any mask or template as well. However, until now, the overall alignment direction of BCP molecules on the Si surface still requires a pre-patterning on Si surface by traditional lithography [20].

**Figure 1.** Schematic processing flow for photolithography: (a) application of photoresist; (b) baking of photoresist; (c) UV-visible light exposure; (d) developing.

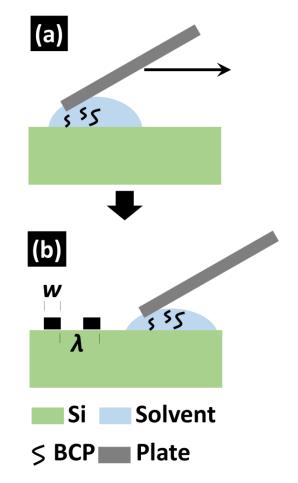

In this work, a novel mask-less pattern formation method, named flow-enabled polymer self-assembly (FESA) is investigated. In FESA, the BCP solution is allowed to dry in a two nearly parallel-plate geometry, in which the lower Si substrate is mounted on a linear translational stage controlled by a computer. Parallel stripes of BCP with high regularity are formed by FESA in a "stop-and-move" mode. First, in the "stop" stage, the lower Si substrate is kept stationary for a short period of time, allowing BCP molecules to self-assemble at the contact line and form a stripe, due to the high evaporative loss of solvent (i.e., toluene) at the edge of the solution. Subsequently, in "move" stage, the lower Si substrate is shifted at a distance  $\lambda$ , making the contact line jump inward to the new position where the second stripe will form. By the iterative "move-and-stop" operation, an array of lines with controlled line width (W) and pitch size ( $\lambda$ ) can be obtained on the Si (Figure 2) [21]. FESA bears significant advantages over the pattern formation methods mentioned above: (1) the pattern dimension as well as its alignment direction can be facilely controlled by intrinsic properties of the BCP molecules as well as the movement of the plate; (2) no mask or template is required, neither should any pre-patterning or physical manipulation, such the UV light or electron beam, be applied. Thus the FESA is a true mask-less pattern formation method; (3) the majority of materials is utilized, in sharp contrast with the spin coating step in photolithography where a considerable amount of materials are wasted; (4) all the processing is completed at room temperature, no heating or cooling is required, nor is any vacuum system needed, thus the energy cost in the production is minimized; (5) since the patterns are formed by a linear movement of the plat, the influence of Si substrate size is minimized, thus good uniformity of pattern geometry can be maintained when scaled up to larger Si wafers.

**Figure 2.** Schematic processing flow for FESA: (a) application of BCP solution into the gap between the plate and Si. The arrow indicates the moving direction of the plate; (b) intermittent moving of the plate and patterns formation (black blocks) with width of w and spacing of  $\lambda$ .

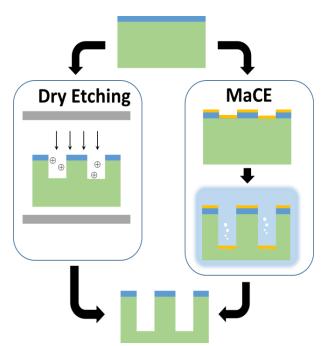

For the microchannels and microgratings fabrication, the pattern formation step is followed by Si etching step. Now the most widely used Si etching for microchannels and microgratings fabrication is the dry etching, or reactive ion etching (RIE). In dry etching, the Si sample is placed between two large electrodes in a gas chamber. Once an electrical power is supplied to the electrode, the gas in the chamber will be ionized and plasma is generated. Under the attack of the plasma, the bare Si surface will be etched and microstructures is formed (Figure 3 left). Dry etching has established the capability of fabricating high aspect ratio microstructures with high pattern transfer fidelity [22, 23]. However, the instruments for dry etching are very expensive.

Recently, a novel Si wet chemical etching method has been reported, which is named as metal-assisted chemical etching (MaCE). In MaCE, a layer of metal catalyst is deposited on the pattern Si surface. The metal-coated Si is then etched by hydrofluoric acid (HF)-hydrogen peroxide (H<sub>2</sub>O<sub>2</sub>) aqueous solution (Figure 3, right). By controlling the metal catalysts' geometry as well as the etching solution composition, nanowires [24], nanopores [25-27] and nanocavity with complicated 3D geometry [28-30] have been successfully fabrication on Si substrates. Especially, the critical conditions for uniform deep trenches and holes etching by MaCE have been identified and fundamentally understood [31, 32]. High aspect ratio microstructures were fabricated with submicrometer accuracy [25, 33, 34]. In the previous MaCE studies, photolithography and electron-beam lithography were used for pattern formation. In this work, we report the successful fabrication of microchannels and microgratings by combining FESA and MaCE. Considering their merit of low cost and excellent performance, the proposed route will be promising for high volume production of microchannels and microgratings.

**Figure 3** Schematic processing flow for dry etching and MaCE.

# 2. Experimental

Single-side polished Si wafers were cut into 2x5 cm<sup>2</sup> pieces and cleaned in piranha solution before the FESA. Poly-(styrene-block-methylmethacrylate) was used as the self-assembly BCP materials for FESA. After FESA, a thin layer of Au was deposited on the patterned Si surface by a Denton Explorer electron beam evaporator. Then the sample was immersed in HF-H<sub>2</sub>O<sub>2</sub> aqueous solution for wet etching. After wet etching, the sample was rinsed by deionized water and dried by nitrogen. The optical microscope image was acquired by an Olympus MX61 microscope. The scanning electron microscope (SEM) images were collected by a Hitachi SU8010 Field-Emission SEM. The cross-sectional SEM was obtained from Si sample after mechanical cleavage.

#### 3. Results and Discussion

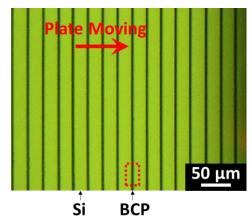

The bare Si surface after FESA is inspected by optical microscope. As shown in Figure 4, straight lines can be clearly observed, which align themselves in perpendicular to the movement of the plate. The width (w) of the lines is measured as 3.0  $\mu$ m, with standard deviation below 0.5  $\mu$ m. The spacing distance ( $\lambda$ ) between two adjacent lines is measured as 25  $\mu$ m. Figure 4 demonstrates that uniform lines can be successfully formed by FESA on bare Si surface with high uniformity. It should be noted that the uniformity of the patterns is sensitive to contamination from the Si surface or BCP solution. In some area where dust particles exist, the lines were found curved.

**Figure 4.** Optical microscope image of Si surface after FESA. The BCP self-assembly appears as black lines and the bare Si surface is presented in green color.

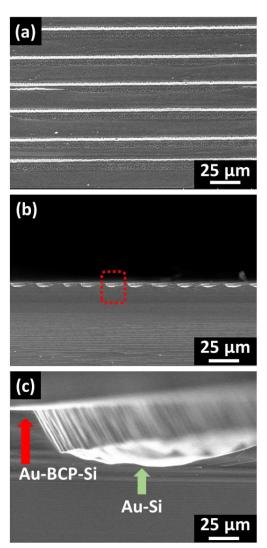

After formation of the pattern, a thin layer of Au was deposited on the Si sample and then the sample was immersed in HF- $H_2O_2$  solution for MaCE. Here we name the area of the Si surface covered by BCP lines as Au-BCP-Si area, and the other area as Au-Si area. As shown in Figure 5 (a), the two areas present sharp contrast under SEM. On the surface of Au-BCP-Si area, the Au layer presents similar morphology to its original morphology before MaCE. In the Au-Si area, however, due to the chemical etching, the surface has a lower brightness and a higher roughness under SEM. The cross-sectional SEM (Figure 5 (b)) further confirms the etching of Si

in the Au-Si area, where microchannels are formed with uniform geometry over the whole sample. The contrast between Au-BCP-Si and Au-Si areas is more clearly elucidated in Figure 5 (c). Si in the Au-BCP-Si protrudes out as microgratings with smooth sidewall. The top surface of Au-BCP-Si area is flat, indicates that no etching occurs in this area. In the Au-Si, the Au catalyst etched into Si with a downward-bending morphology, and microchannels are formed. Geometric parameters of the Si sample after FESA and MaCE are listed in Table 1. The results demonstrate that the BCP, once self-assembled, possess sufficient adhesion with the Si surface. More importantly, the results indicate that the BCP bears good chemical stability in the HF-H<sub>2</sub>O<sub>2</sub> etchant solution as well as good capability in blocking the etching of underneath Si from Au. In other words, BCP serves as both excellent pattern-formation material in FESA as well as the etching mask materials with high etching selectivity over Si in MaCE. In comparison, in dry etching, the pattern formation material, either photoresist or BCP, can hardly be used as the etching mask, because most polymeric materials are unable to withstand long-time exposure in plasma. Another layer of hard mask, such as silicon dioxide[35], chromium [36] or aluminum [7] are always requied for dry etching, which add cost to the overall processing.

**Table 1** Geometric parameters of the Si sample after FESA and MaCE, respectively

| Parameter                | Value        |  |

|--------------------------|--------------|--|

| Initial BCP Line Width   | 3.0 µm       |  |

| Initial BCP Line Spacing | 25 μm        |  |

| BCP Line After MaCE      | 3.0 µm       |  |

| Microchannel Depth       | 2.2 μm       |  |

| Microchannel Width       | 14.5 μm      |  |

| Sidewall Tapering Angle  | $30^{\circ}$ |  |

## Conclusion

In summary, formation of micro-pattern by the combination of FESA of BCP is demonstrated. The pattern shows good geometric uniformity. The pattern-formation material, BCP, serves as a good etching mask material in the following MaCE step, which successfully fabricates microchannels and microgratings on Si substrate. Compared to the traditional routes, the results of this work indicate that the combination of FESA and MaCE is a promising approach for high-volume production of microchannels and microgratings with simplicity of processing, cost efficiency and environmental-friendliness.

# Acknowledgments

The authors thank the National Science Foundation (NSF CMMI 1130876) for the funding support.

**Figure 5.** (a) Top-view and (b) cross-sectional scanning electron microscope (SEM) images of a Si sample after FESA and MaCE. (c) shows the magnified image of circled area in (b).

## References

- 1. C. R. King, D. Sekar, M. S. Bakir, B. Dang, J. Pikarsky, and J. D. Meindl, "3D stacking of chips with electrical and microfluidic I/O interconnects," in *Electronic Components and Technology Conference*, 2008. ECTC 2008. 58th, Orlando, Florida, 2008, pp. 1-7.

- 2. A. Nomerotski, J. Buytart, P. Collins, R. Dumps, E. Greening, M. John, A. Mapelli, A. Leflat, Y. Li, G. Romagnoli, and B. Verlaat, "Evaporative CO 2 cooling using microchannels etched in silicon for the future LHCb vertex detector," *J. Inst.*, vol. 8, p. P04004, 2013.

- 3. G. M. Whitesides, "The origins and the future of microfluidics," *Nature*, vol. 442, pp. 368-373, 07/27/print 2006.

- 4. M. W. Losey, R. J. Jackman, S. L. Firebaugh, M. A. Schmidt, and K. F. Jensen, "Design and fabrication of

- microfluidic devices for multiphase mixing and reaction," *J. Microelectromech. Systems.*, vol. 11, pp. 709-717, 2002.

- 5. F. Ayazi and K. Najafi, "A HARPSS polysilicon vibrating ring gyroscope," *J. Microelectromech. Syst.*, vol. 10, pp. 169-179, Jun 2001.

- 6. F. Ayazi and K. Najafi, "High aspect-ratio combined poly and single-crystal silicon (HARPSS) MEMS technology," *J. Microelectromech. Syst.*, vol. 9, pp. 288-294, 2000.

- 7. F. Marty, L. Rousseau, B. Saadany, B. Mercier, O. Francais, Y. Mita, and T. Bourouina, "Advanced etching of silicon based on deep reactive ion etching for silicon high aspect ratio microstructures and three-dimensional micro- and nanostructures," *Microelectron. J.*, vol. 36, pp. 673-677, Jul 2005.

- 8. G. Roelkens, D. Van Thourhout, and R. Baets, "High efficiency Silicon-on-Insulator grating coupler based on a poly-Silicon overlay," *Opt. Express*, vol. 14, pp. 11622-11630, 2006/11/27 2006.

- 9. D. Taillaert, P. Bienstman, and R. Baets, "Compact efficient broadband grating coupler for silicon-on-insulator waveguides," *Opt. Lett.*, vol. 29, pp. 2749-2751, 2004/12/01 2004.

- 10. S. Y. Chou, P. R. Krauss, and P. J. Renstrom, "Imprint Lithography with 25-Nanometer Resolution," *Science*, vol. 272, pp. 85-87, April 5, 1996 1996.

- 11. C. M. Sotomayor Torres, S. Zankovych, J. Seekamp, A. P. Kam, C. Clavijo Cedeño, T. Hoffmann, J. Ahopelto, F. Reuther, K. Pfeiffer, G. Bleidiessel, G. Gruetzner, M. V. Maximov, and B. Heidari, "Nanoimprint lithography: an alternative nanofabrication approach," *Mater. Sci. Eng. C*, vol. 23, pp. 23-31, 1/15/2003.

- 12. Y. Xia and G. M. Whitesides, "Soft Lithography," *Annu. Rev. Mater. Sci.*, vol. 28, pp. 153-184, 1998.

- 13. Y. Xia, J. Tien, D. Qin, and G. M. Whitesides, "Non-Photolithographic Methods for Fabrication of Elastomeric Stamps for Use in Microcontact Printing," *Langmuir*, vol. 12, pp. 4033-4038, 1996/01/01 1996.

- 14. K. Peng, M. Zhang, A. Lu, N.-B. Wong, R. Zhang, and S.-T. Lee, "Ordered silicon nanowire arrays via nanosphere lithography and metal-induced etching," *Appl. Phys. Lett.*, vol. 90, p. 163123, 2007.

- 15. C. L. Haynes and R. P. Van Duyne, "Nanosphere Lithography: A Versatile Nanofabrication Tool for Studies of Size-Dependent Nanoparticle Optics," *J. Phys. Chem. B*, vol. 105, pp. 5599-5611, 2001/06/01 2001.

- 16. C. L. Cheung, R. J. Nikolić, C. E. Reinhardt, and T. F. Wang, "Fabrication of nanopillars by nanosphere lithography," *Nanotechnology*, vol. 17, p. 1339, 2006.

17. C. J. Hawker and T. P. Russell, "Block Copolymer Lithography: Merging "Bottom-Up" with "Top-Down" Processes," *MRS Bulletin*, vol. 30, pp. 952-966, 2005.

- 18. C. M. Bates, M. J. Maher, D. W. Janes, C. J. Ellison, and C. G. Willson, "Block Copolymer Lithography," *Macromolecules*, vol. 47, pp. 2-12, 2014/01/14 2013.

- 19. X. Gu, Z. Liu, I. Gunkel, S. T. Chourou, S. W. Hong, D. L. Olynick, and T. P. Russell, "High Aspect Ratio Sub-15 nm Silicon Trenches From Block Copolymer Templates," *Adv. Mater.*, vol. 24, pp. 5688-5694, 2012.

- 20. S.-J. Jeong, H.-S. Moon, B. H. Kim, J. Y. Kim, J. Yu, S. Lee, M. G. Lee, H. Choi, and S. O. Kim, "Ultralarge-Area Block Copolymer Lithography Enabled by Disposable Photoresist Prepatterning," *ACS Nano*, vol. 4, pp. 5181-5186, 2010/09/28 2010.

- 21. B. Li, W. Han, B. Jiang, and Z. Lin, "Crafting Threads of Diblock Copolymer Micelles via Flow-Enabled Self-Assembly," *ACS Nano*, vol. 8, pp. 2936-2942, 2014/03/25 2014.

- 22. J. Yeom, Y. Wu, J. C. Selby, and M. A. Shannon, "Maximum achievable aspect ratio in deep reactive ion etching of silicon due to aspect ratio dependent transport and the microloading effect," *J. Vac. Sci. Technol. B*, vol. 23, pp. 2319-2329, 2005.

- 23. J. Parasuraman, A. Summanwar, F. Marty, P. Basset, D. E. Angelescu, and T. Bourouina, "Deep reactive ion etching of sub-micrometer trenches with ultra high aspect ratio," *Microelectron. Eng.*, vol. 113, pp. 35-39, Jan 2014.

24. Z. Huang, N. Geyer, P. Werner, J. de Boor, and U. Gösele, "Metal-Assisted Chemical Etching of Silicon: A Review," *Adv. Mater.*, vol. 23, pp. 285-308, 2011.

25. L. Li and C. P. Wong, "High aspect ratio sub-100 nm silicon vias (SVs) by metal-assisted chemical etching (MaCE) and copper filling," in *Electronic Components and*

- 2326-2331.

26. L. Li and C.-P. Wong, "High-speed wet etching of through silicon vias (TSVs) in micro- and nanoscale," in *Electronic Components and Technology Conference (ECTC)*, 2014 IEEE 64th, 2014, pp. 631-635.

Technology Conference (ECTC), 2013 IEEE 63rd, 2013, pp.

- 27. X. Li and P. W. Bohn, "Metal-assisted chemical etching in  $HF/H_2O_2$  produces porous silicon," *Appl. Phys. Lett.*, vol. 77, pp. 2572-2574, 2000.

- 28. O. J. Hildreth, A. G. Fedorov, and C. P. Wong, "3D Spirals with Controlled Chirality Fabricated Using Metal-Assisted Chemical Etching of Silicon," *ACS Nano*, vol. 6, pp. 10004-10012, 2012.

- 29. O. J. Hildreth, W. Lin, and C. P. Wong, "Effect of Catalyst Shape and Etchant Composition on Etching Direction in Metal-Assisted Chemical Etching of Silicon to Fabricate 3D Nanostructures," *ACS Nano*, vol. 3, pp. 4033-4042, 2009.

30. O. J. Hildreth, D. Brown, and C. P. Wong, "3D Out-of-

- 30. O. J. Hildreth, D. Brown, and C. P. Wong, "3D Out-of-Plane Rotational Etching with Pinned Catalysts in Metal-Assisted Chemical Etching of Silicon," *Adv. Funct. Mater.*, vol. 21, pp. 3119-3128, 2011.

- 31. L. Li, Y. Liu, X. Zhao, Z. Lin, and C.-P. Wong, "Uniform Vertical Trench Etching on Silicon with High Aspect Ratio by Metal-Assisted Chemical Etching Using Nanoporous Catalysts," *ACS Appl. Mater. Interfaces*, vol. 6, pp. 575-584, 2014/01/08 2014.

- 32. L. Li, X. Zhao, and C.-P. Wong, "Deep Etching of Single-and Polycrystalline Silicon with High Speed, High Aspect Ratio, High Uniformity, and 3D Complexity by Electric Bias-Attenuated Metal-Assisted Chemical Etching (EMaCE)," *ACS Appl. Mater. Interfaces*, vol. 6, pp. 16782-16791, 2014/10/08 2014.

- 33. L. Li, Y. Yao, Z. Lin, Y. Liu, and C. P. Wong, "Low-cost micrometer-scale silicon vias (SVs) fabrication by metal-assisted chemical etching (MaCE) and carbon nanotubes

- (CNTs) filling," in *Electronic Components and Technology Conference (ECTC), 2013 IEEE 63rd*, 2013, pp. 581-585.

34. L. Li and C.-P. Wong, "Wet etching of deep trenches on silicon with three-dimensional (3D) controllability," in *Electronic Components and Technology Conference (ECTC), 2014 IEEE 64th*, 2014, pp. 1848-1852.

- 35. J. L. A. Yeh, J. Hongrui, and N. C. Tien, "Integrated polysilicon and DRIE bulk silicon micromachining for an electrostatic torsional actuator," *J. Microelectromech. Syst.*, vol. 8, pp. 456-465, 1999.

- 36. L. Jian, M. P. Brenner, J. H. Lang, A. H. Slocum, and R. Struempler, "DRIE-fabricated curved-electrode zipping actuators with low pull-in voltage," in *Transducers, Solid-State Sensors, Actuators and Microsystems, 12th International Conference on, 2003*, 2003, pp. 480-483 vol.1.